Applying dual core lockstep in embedded processors to mitigate radiation induced soft errors | Semantic Scholar

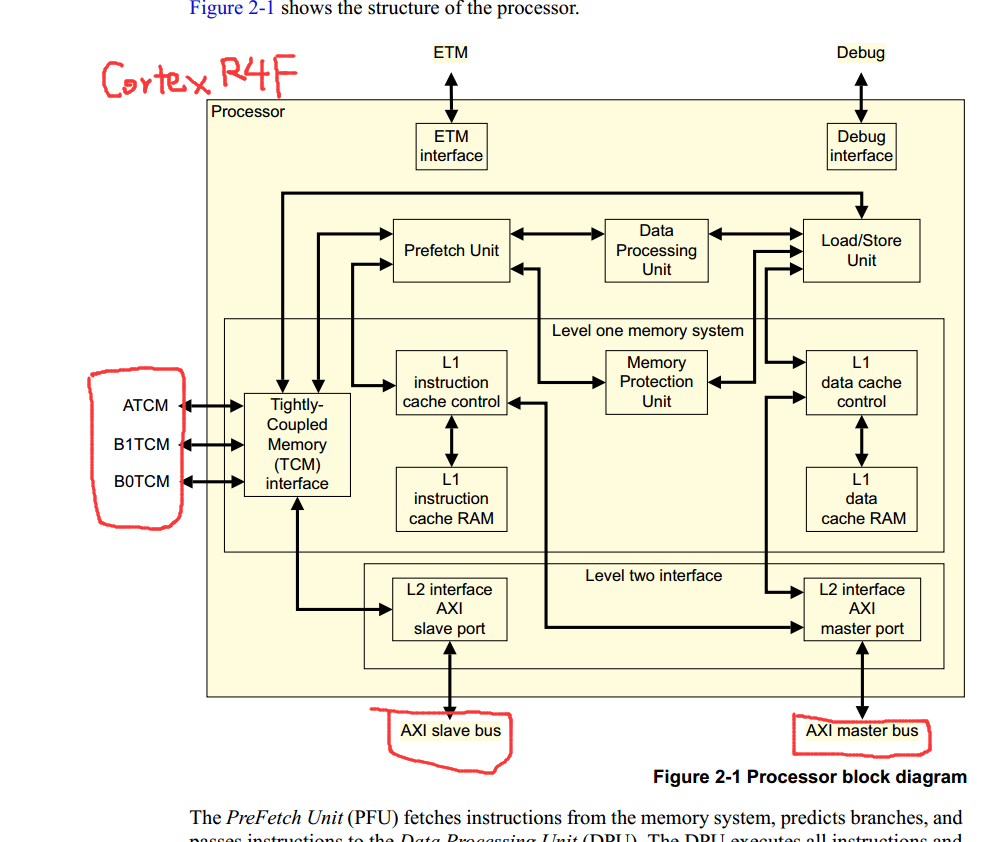

Figure 1 from A Triple Core Lock-Step (TCLS) ARM® Cortex®-R5 Processor for Safety-Critical and Ultra-Reliable Applications | Semantic Scholar

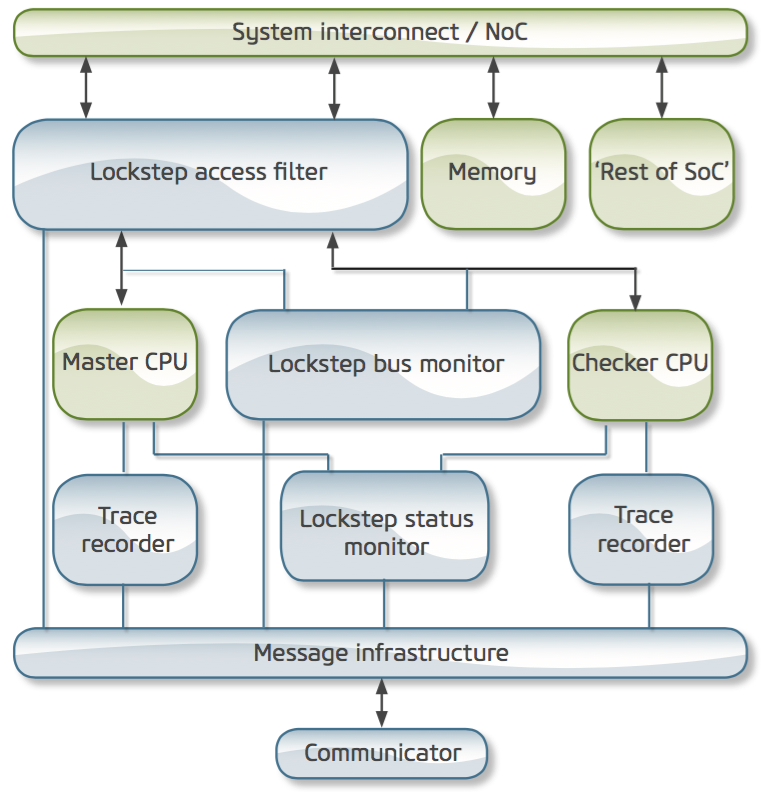

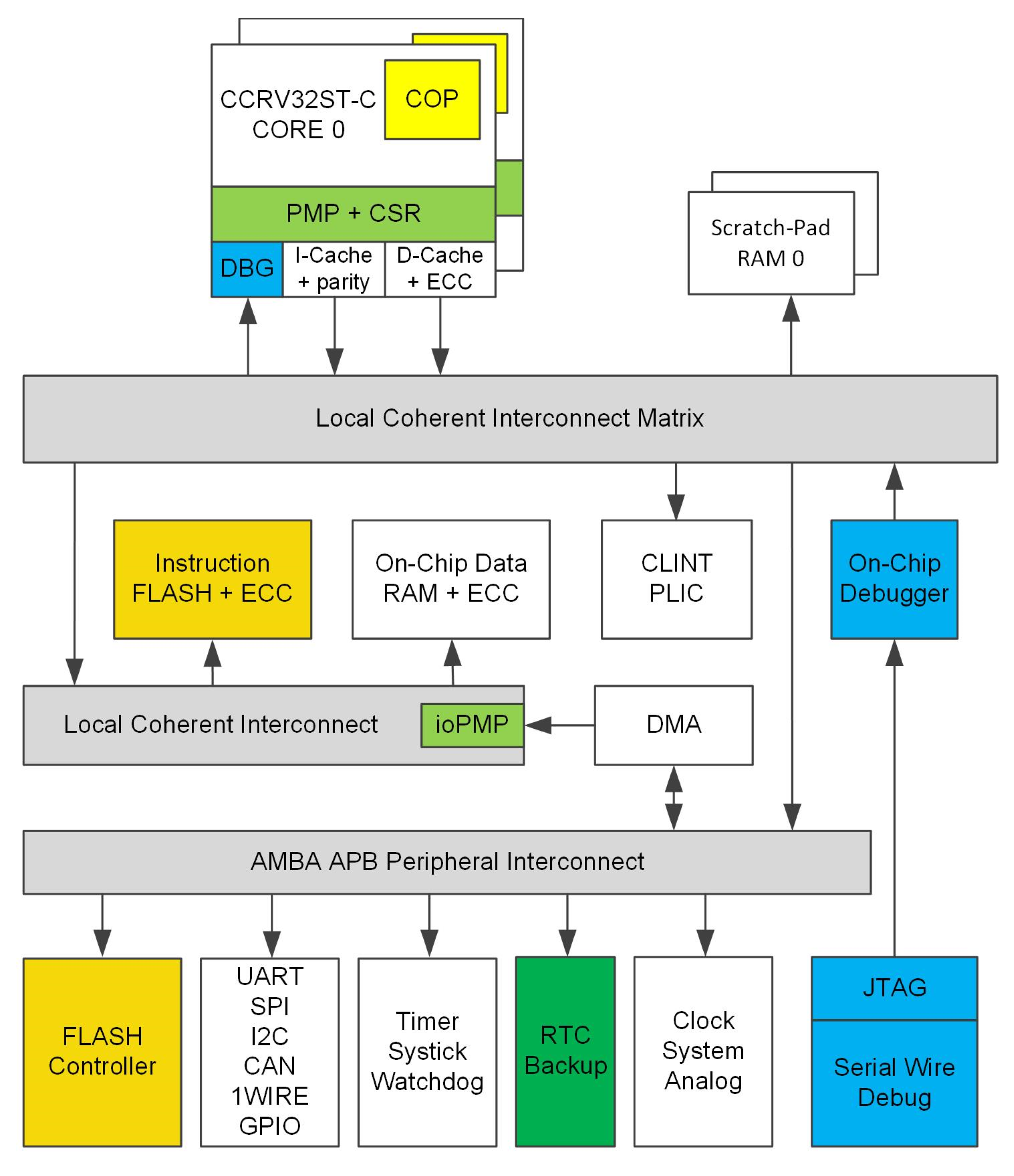

Dual-core lockstep processors with integrated safety monitors help hit high automotive safety levels

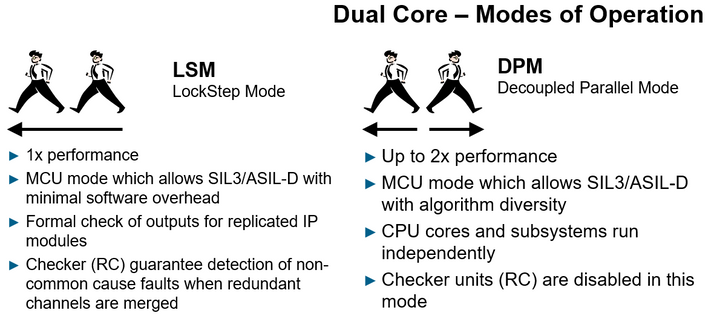

Comparing Lock-Step, redundant execution & Split-Lock - Embedded blog - Arm Community blogs - Arm Community

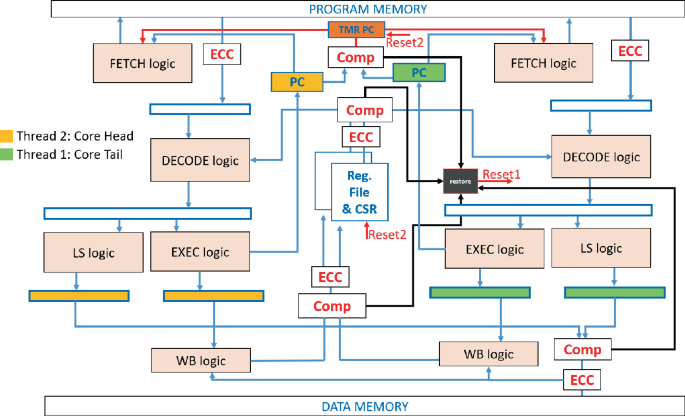

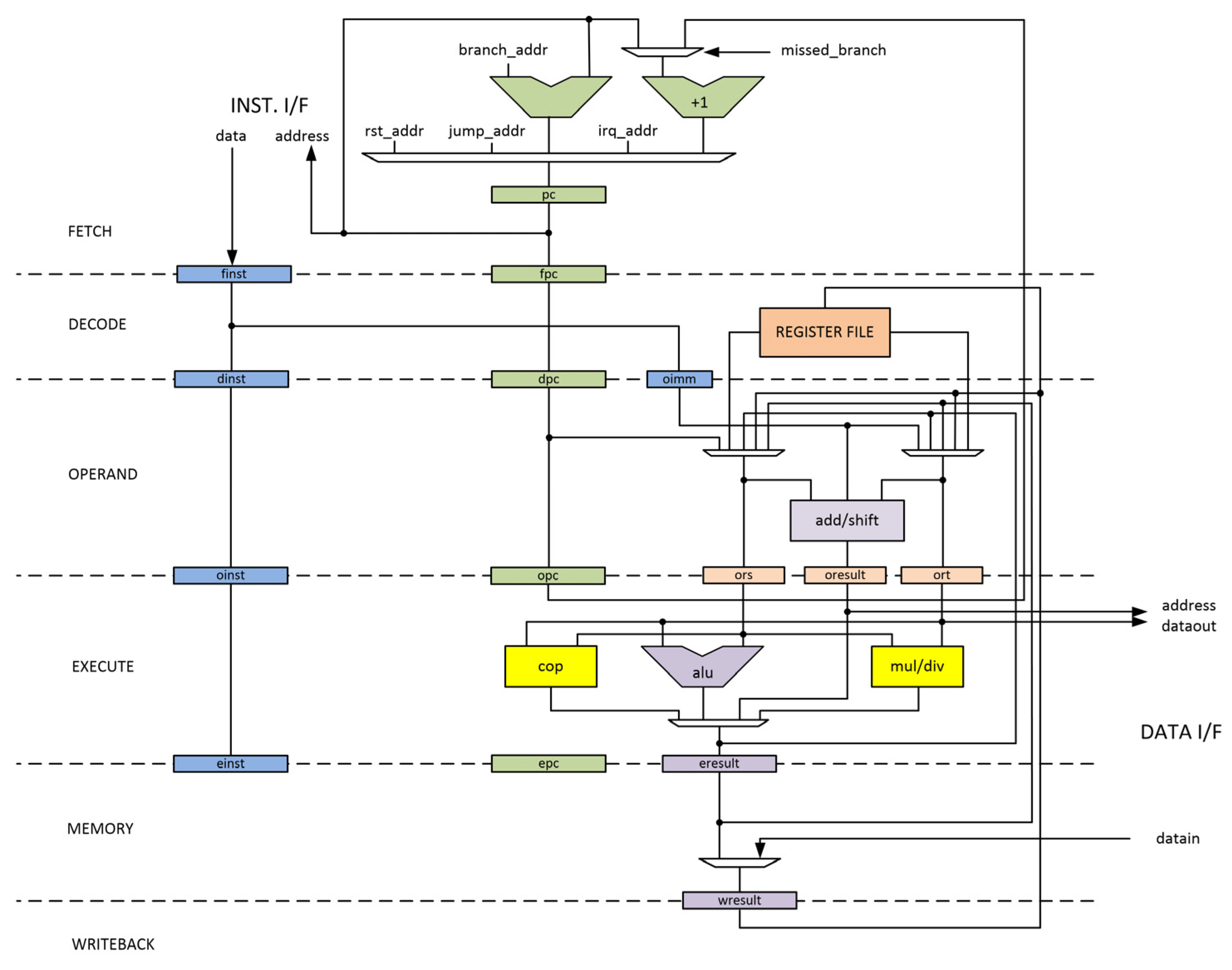

Electronics | Free Full-Text | Variable Delayed Dual-Core Lockstep (VDCLS) Processor for Safety and Security Applications

Figure 2 from A Triple Core Lock-Step (TCLS) ARM® Cortex®-R5 Processor for Safety-Critical and Ultra-Reliable Applications | Semantic Scholar

Electronics | Free Full-Text | Variable Delayed Dual-Core Lockstep (VDCLS) Processor for Safety and Security Applications